# Implementation of Single Chip 28 GHz SPDT Switch-less Front-end Circuits in a 65nm CMOS process

Seunghyn Jang RF technology team ETRI Daejeon, South Korea damduk@etri.re.kr

Bonghyuk Park RF technology team ETRI Daejeon, South Korea <u>bhpark@etri.re.kr</u> Sunwoo Kong RF technology team ETRI Daejeon, South Korea swkong@etri.re.kr

Kwang-Seon Kim RF technology team ETRI Daejeon, South Korea gskim@etri.re.kr Hui-Dong Lee RF technology team ETRI Daejeon, South Korea <u>leehd@etri.re.kr</u>

Jung-Hwan Hwang RF technology team ETRI Daejeon, South Korea jhhwang@etri.re.kr

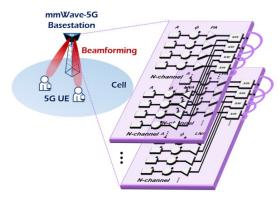

Fig. 1. RF front-ends in mmWave beamforming modules for 5G mobile communication

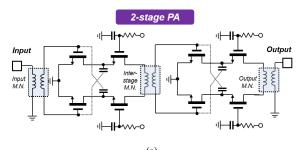

Fig. 2. Block diagrams: (a) power amplifer, (b) low-noise amplifer

a single-chip 28 GHz SPDT-less front-end IC for 5G mobile communication services. The focus of the present paper is on investigating the implementation performance of a low-loss RF front-end architecture eliminating the SPDT switch in a conventional front-end. According to the measurement results, the SPDT-less design shows negligible loss at the output stage and hence higher output power. The fabricated CMOS chip exhibits excellent performance, with a peak gain of 20.8 dB and a 3-dB bandwidth of 4 GHz (28 GHz – 32 GHz) in the Tx-mode. In Rx-mode, a wider bandwidth characteristic of 7.4 GHz (25.6 GHz – 33 GHz) and a peak gain of 18.9 dB are observed. The overall results demonstrate the potential of the SPDT-less front-end for efficient reception and future low-loss RF front-end designs

Abstract— This paper presents the implementation results of

## Keywords—5G, 28GHz, mobile communication, FEM, frontend module, beamforming

## I. INTRODUCTION

In recent years, significant efforts have been made to deploy fifth-generation (5G) mobile communication services [1-3, 6-8, 10-15] using the 28 GHz frequency-band[6-8, 10-13]. However, as the frequency increases, the power consumption for the signal amplification dramatically rises, highlighting the need for research on low-loss RF front-end architectures. In this paper, as part of these ongoing efforts, the implementation results of a single-chip 28 GHz SPDT (Single-Pole Double-Throw) switch-less front-end IC on a standard 65nm CMOS process are provided. By eliminating the SPDT switch required in a conventional RF front-end, as shown Fig. 1, the loss of the output stage of the SPDT-less front-end was negligible and, as a result, enhance the output power level[12].

## II. SPDT SWITCH-LESS FRONT-END

The 28GHz SPDT-less front-end circuits have been designed on a standard CMOS 65nm process. As shown in Fig. 2(a), the power amplifier in the front-end has two-stage differential cascode structure and four neutralized capacitors. With the neutralized capacitors, the stability problem of the power amplifier is relieved[4-5]. For the input, output and inter-stage matchings, transformers are designed for small size and low loss. The structure of the LNA is illustrated in Fig. 2(b). The LNA has three-stage common-source structure with

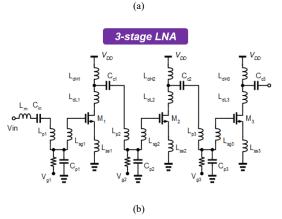

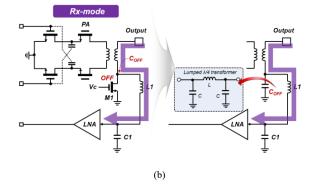

Fig. 3. Operation principle of SPDT-less front-end circuits: (a)Txmode, (b) Rx-mode

several transformer matching circuits and transformer output load[7].

The architecture and basic operation principles of the SPDT-less front-end are depicted in Fig. 3[12]. By using the PA output transformer as one block of a transmit/receive(T/R) switch network and then eliminate a lossy SPDT switch, the T/R switching structure can be simple. For Tx-mode, M1 is ON and the one of the secondary winding of the PA output transformer is connected to GND, which is virtually the same architecture of the PA itself. For Rx-mode, M1 is OFF, the signal from the output PAD to the LNA input experiences the secondary winding of the PA output transformer and the C-L-C network consisting of C<sub>OFF</sub> of M1, L1 and C1, as shown in Fig. 3(b). Since the C-L-C network is a  $\lambda/4$  transformer, it can be used as a matching network for LNA input and reduce the number of LNA input matching components.

## **III. MEASUREMENT RESULTS**

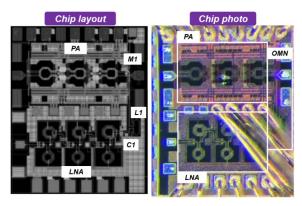

The designed SPDT-less front-end chip has been fabricated in a CMOS 65nm process, and the size of the chip is 720 $\mu$ m x 910 $\mu$ m including PADs, as shown Fig. 4. The PADs in the middle of the chip are for additional GNDs.

Fig. 5 shows the measurement results of the Tx-mode of the chip. The PA was biased with VDD of 1.8V, 1.3V for cascode-stages, and 0.445V for the 1st and 2nd common-source stages, resulting in a quiescent current of 93 mA. The peak gain of 20.8 dB was observed at around 30 GHz with a 3-dB bandwidth of 4 GHz (28 GHz – 32 GHz). Overall, it was slightly optimized for frequencies slightly higher than 28 GHz. Although the Tx-mode front-end chip exhibits relatively broad frequency characteristics, it is necessary to achieve a

Fig. 4. Chip layout and photo graph of the 28 GHz CMOS SPDT-less front-end chip

Fig. 5. Measurement results of the Tx-mode of the fabricated front-end chip: (a) S21, (b) S11 and S22, and (c) power, gain and PAE

wider bandwidth for the input/output matching of the power amplifier in order to provide more margin for PVT (process, voltage, temperature) variations. This is an important aspect to consider and will be addressed in future designs. To investigate the output power characteristics of the transmitter, a one-tone test was conducted, and the measurement results are presented in Fig. 5(c). The maximum efficiency exhibited was 11%, and the maximum output power was greater than 15.5 dBm. The gain was greater than 20.5 dB, but it showed a rapid decline in gain, resulting in a measured output P1dB of 12.5 dBm.

Fig. 6. Measurement results of the Rx-mode of the fabricated frontend chip: (a) S12, (b) S11 and S22

The measured S-parameter performance of the Rx-mode of the front-end chip is shown in Fig. 6. The receiver consumes 15 mA from a 1.2V supply. In Fig. 6(a), the measured Rx-mode gain is depicted. Compared to the Tx-mode, the receiver demonstrates a wider bandwidth characteristic with the 3-dB bandwidth of 7.4 GHz(25.6 GHz – 33.0 GHz) with a peak gain of 18.9 dB. Unfortunately, we were unable to measure the noise figure of the Rx-mode of the chip. The EM simulation provided the noise figure of the Rx-mode was around 5.4 dB, and the noise figure of the LNA itself was approximately 3 dB.

The summary of the measurement results of the fabricated 28 GHz SPDT-less CMOS front-end chip was shown in Table I.

| T/R<br>Mode | Fabricated SPDT-less 28GHz FEM chip |                                         |

|-------------|-------------------------------------|-----------------------------------------|

|             | Parameter                           | Measurement                             |

| Tx-mode     | Frequency                           | $28 \ \mathrm{GHz} - 32 \ \mathrm{GHz}$ |

|             | Maximum gain                        | 20.8 dB                                 |

|             | Input/Output return losses          | < -8.8 dB (Input)<br>< -5.4 dB (Output) |

|             | Maximum output power                | 15.5 dBm                                |

| Rx-mode     | Frequency                           | 25.6 GHz – 33 GHz                       |

|             | Maximum gain                        | 18.9 dB                                 |

|             | Input/Output return losses          | < -12 dB (Input)<br>< -14 dB (Output)   |

|             | Noise figure <sup>a</sup>           | 5.4 dB                                  |

TABLE I. PERFORMANCE SUMMARY

a. EM simulation result

#### IV. CONCLUSION

In the present paper, the implementation results of the 28 GHz SPDT-less front-end IC were provided and discussed. The Tx-mode of the chip exhibited the maximum output power of over 15.5 dBm, making it suitable for 5G mobile communication services. The Rx-mode demonstrated a wider bandwidth characteristic and a peak gain of 18.9 dB,

indicating its potential for efficient reception in the designated frequency range. Further research is required to measure the noise figure of the Rx-mode, but the overall performance of the SPDT-less front-end chip highlights its potential for low-loss RF front-end architectures in future designs.

#### ACKNOWLEDGMENT

This work was supported by Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (2021-0-00938, Development of THz RF core component)

#### REFERENCES

- Lee, Hongtak, et al., "A hybrid polar-LINC CMOS power amplifier with transmission line transformer combiner." IEEE transactions on microwave theory and techniques 61.3 (2013): 1261-1271.

- [2] Jang, Seunghyun, et al. "A 2.6-GHz partial-envelope delta-sigmadigitized carrier-bursting transmitter." IEEE Microwave and Wireless Components Letters 30.7 (2020): 697-700.

- [3] S. Jang, et al., "Digital radio-over-fiber system with multi-pulse Manchester encoding-assisted delta-sigma modulation," Opt. Express, vol. 26, no. 7, pp. 8335-8349, 2017

- [4] H. Jeong, H. D. Lee, B. Park, S. Jang, S. Kong and C. Park, "Three-Stacked CMOS Power Amplifier to Increase Output Power With Stability Enhancement for mm-Wave Beamforming Systems," in IEEE Transactions on Microwave Theory and Techniques, vol. 71, no. 6, pp. 2450-2464, June 2023, doi: 10.1109/TMTT.2022.3228539.

- [5] Yang, Junhyuk, et al. "Ku-Band CMOS Power Amplifier with Three-Stack Power Stage to Enhance Output Power and Efficiency." Applied Sciences 12.9 (2022): 4432.

- [6] B. Park, H. -D. Lee, S. Jang, S. Kong, S. Wang and S. -B. Hyun, "A 28GHz-band integrated GaAs Power Amplifier for 5G Mobile Communications," 2022 19th International SoC Design Conference (ISOCC), Gangneung-si, Korea, Republic of, 2022, pp. 376-377, doi: 10.1109/ISOCC56007.2022.10031407.

- [7] S. Kong, H. -D. Lee, S. Jang, J. Park, K. -S. Kim and K. -C. Lee, "A 28-GHz CMOS LNA with Stability-Enhanced Gm-Boosting Technique Using Transformers," 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019, pp. 7-10, doi: 10.1109/RFIC.2019.8701753.

- [8] S. Jang, et al., "28 GHz 1.8 dB Insertion Loss SPDT Switch with 24 dB Isolation in 65 nm CMOS," in *European Microwave Conference (EuMC)*, paper 43-1, 2018.

- [9] T. Kim, H. D. Lee, B. Park, S. Jang, S. Kong and C. Park, "Design of a K-Band High-Linearity Asymmetric SPDT CMOS Switch Using a Stacked Transistor," in IEEE Microwave and Wireless Components Letters, vol. 32, no. 12, pp. 1443-1446, Dec. 2022, doi: 10.1109/LMWC.2022.3192440.

- [10] S. Jang, S. Kong, H. -D. Lee, J. Park, K. -S. Kim and B. Park, "A 28 GHz >30 dBm Output P1dB SPDT switch with integrated ESD protection in CMOS 65 nm," 2020 50th European Microwave Conference (EuMC), Utrecht, Netherlands, 2021, pp. 140-143, doi: 10.23919/EuMC48046.2021.9338227.

- [11] J. Park, S. Lee, D. Lee and S. Hong, "9.8 A 28GHz 20.3%-Transmitter-Efficiency 1.5°-Phase-Error Beamforming Front-End IC with Embedded Switches and Dual-Vector Variable-Gain Phase Shifters," 2019 IEEE International Solid- State Circuits Conference - (ISSCC), 2019, pp. 176-178, doi: 10.1109/ISSCC.2019.8662512.

- [12] Kamran Entesari et al., "CMOS Front-End for 28 GHz 5G Terminals", IEEE IMS workshop WFJ-3, Jun. 2017.

- [13] Lee, Hui Dong, et al. "A miniatured 28-GHz FEM using a 0.15-μm InGaAs/GaAs E-mode pHEMT process." 2019 14th European Microwave Integrated Circuits Conference (EuMIC). IEEE, 2019.

- [14] S. Wang, J. Park and S. Hong, "A K-Band Variable-Gain Phase Shifter Based on Gilbert-Cell Vector Synthesizer With RC–RL Poly-Phase Filter," in IEEE Microwave and Wireless Components Letters, vol. 31, no. 4, pp. 393-396, April 2021, doi: 10.1109/LMWC.2021.3056881.

- [15] Park, Jeehoon, et al. "Design of 6-Bit 28GHz Phase Shifter in 65NM CMOS." 2018 Asia-Pacific Microwave Conference (APMC). IEEE, 2018.